# **JW1565**

# Offline QR GaN Flyback Converter

Preliminary Specifications Subject to Change without Notice

#### DESCRIPTION

JW1565 is an isolated offline flyback PWM converter with GaN integrated, which features quasi-resonant (QR) operation. QR control improves efficiency by reducing switching loss and benefits EMI performance with nature frequency variation, and an internal maximum frequency limitation to overcome the inherent disadvantages of QR Flyback.

JW1565 comprises a HV pin for startup to eliminate conventional startup resistor and save standby mode energy consumption. It can comply with the most stringent efficiency regulations. Also, the HV pin is used for X-cap discharge when the AC input is removed, which helps to reduce the X-cap discharge loss and achieve extremely low standby power loss.

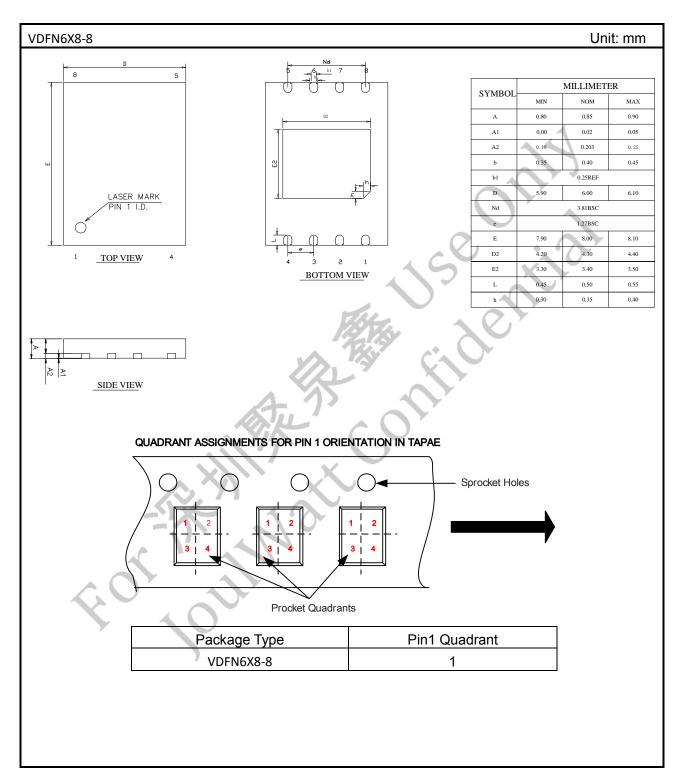

JW1565 is available in the 6mm\*8mm VDFN package. The high level of integration results in a simple to use, low component count, and high efficiency application solution for isolated power delivery.

Company's Logo is Protected, "JW" and "JOULWATT" are Registered Trademarks of Joulwatt Technology Co.,Ltd.

### **FEATURES**

- Built-in High Voltage Start-up (700V)

- Integrated 650V GaN

- X-Capacitor Discharge Function

- Wider VDD Operation Range (Up to 90V)

- QR Operation for High Efficiency

- Maximum 260kHz Switching Frequency

- Optional OCP and OPP Function for Different PD and QC Output Application

- Very Low Standby Power Consumption

- Cycle-By-Cycle Current Limit

- Reliable Fault Protections: VDD OVP, VS OVP and UVP, Brown-In and Brown-Out, CS Open Protection, OCP, OPP, Internal OTP

- Frequency Jitter to Ease EMI Compliance

- VDFN6X8-8 Package

### **APPLICATIONS**

- PD and Quick-Charging Chargers

- AC/DC Adapters with Wide Output Range

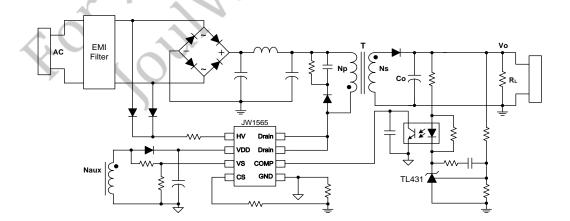

### TYPICAL APPLICATION

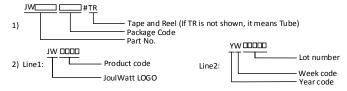

### **ORDER INFORMATION**

| DEVICE <sup>1)</sup> | PACKAGE             | TOP MARKING <sup>2)</sup> | ENVIRONMENTAL <sup>3)</sup> |  |

|----------------------|---------------------|---------------------------|-----------------------------|--|

| JW1565VDFNF#TR       | VDFN6X8-8           | JW1565                    | Green                       |  |

| JW 1303 / DFMF# I K  | V D F I N U N O - O | YW□□□□                    | Green                       |  |

#### Notes:

${\bf 3)} \ All \ JoulWatt \ products \ are \ packaged \ with \ Pb-free \ and \ Halogen-free \ materials \ and \ compliant to \ RoHS \ standards.$

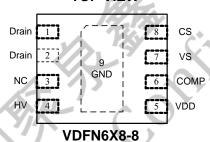

### **PIN CONFIGURATION**

### **TOP VIEW**

# ABSOLUTE MAXIMUM RATING<sup>1)</sup>

| Drain Pin                                                 | 650V                                             |

|-----------------------------------------------------------|--------------------------------------------------|

| HV Pin                                                    | 700V                                             |

| VDD Pin                                                   | 100V                                             |

| COMP, CS Pin                                              | 0.3V to 5V (5V to 5.5V<10us)                     |

| VS Pin                                                    | 0.3V to 5V (-0.7V to -0.3<10us, 5V to 5.5V<10us) |

| Junction Temperature <sup>2)3)</sup>                      | 150°C                                            |

| Storage Temperature                                       | 65°C to +150°C                                   |

| Lead Temperature (Soldering, 10sec)                       | 260°C                                            |

| Continuous Power Dissipation (TA = +25 °C) <sup>4</sup> ) | 2.5W                                             |

2022/04/26

### RECOMMENDED OPERATING CONDITIONS

| VDD Voltage                                      | 8 to 88V                                        |

|--------------------------------------------------|-------------------------------------------------|

| Operating Junction Temperature (T <sub>J</sub> ) | 40°C to 125°C                                   |

| THERMAL PERFORMANCE <sup>5)</sup>                | $oldsymbol{	heta}_{JA}$ $oldsymbol{	heta}_{JC}$ |

| VDFN6X8-8                                        | 25.52.3°C/W                                     |

#### Note:

- 1) Exceeding these ratings may damage the device. These stress rating do not imply function operation of the device at any other conditions beyond those indicated under RECOMMENDED OPERATING CONDITIONS.

- 2) The JW1565 includes thermal protection that is intended to protect the device in overload conditions. Continuous operation over the specified absolute maximum operating junction temperature may damage the device.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) The maximum allowable continuous power dissipation at any ambient temperature is calculated by PD (MAX) = ( TJ (MAX)-TA)/ $\theta$ JA.

- 5) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$T_A$ =25°C, unless otherwise stated

Advance Information, not production data, subject to change without notice.

| ITEM                                           | SYMBOL               | CONDITION                           | MIN. | TYP. | MAX.  | UNITS    |

|------------------------------------------------|----------------------|-------------------------------------|------|------|-------|----------|

| High Voltage Section (HV Pin)                  |                      |                                     |      |      |       |          |

| Supply Current from HV Pin                     | l <sub>HV</sub>      | V <sub>HV</sub> =120 V, VDD=0 V     |      | 3    |       | mA       |

| Leakage Current of HV Pin                      | I <sub>HV_LK</sub>   | V <sub>HV</sub> =500 V, VDD=20V     |      | 20   |       | uA       |

| Brown-In Threshold                             | V <sub>BR_IN</sub>   |                                     | 103  | 111  | 119   | V        |

| Brown-Out Threshold                            | V <sub>BR_OUT</sub>  |                                     |      | 98   |       | V        |

| Brown-Out Blanking Time <sup>7)</sup>          | t <sub>BR_OUT</sub>  |                                     |      | 70   | -     | ms       |

| Supply Voltage Section (VDD F                  | Pin)                 |                                     |      |      |       |          |

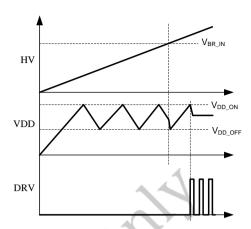

| Turn-On Threshold Voltage                      | $V_{DD\_ON}$         | VDD Rising, TA = 25°C               | 6.8  | 7.4  | 8     | V        |

| Turn-Off Threshold Voltage                     | V <sub>DD_OFF</sub>  | VDD Falling, TA = 25°C              | 3.8  | 4.7  | 5.6   | V        |

| Reset Threshold Voltage                        | $V_{DD\_RST}$        |                                     | 2.5  | 3    | 3.5   | V        |

| Startup Current                                | I <sub>DD_ST</sub>   | VDD=V <sub>DD_ON</sub> -0.5 V       | A () | 300  |       | uA       |

| Operating Supply Current                       | I <sub>DD_OP</sub>   | VDD=20 V, fs=260kHz                 |      | 0.9  |       | mA       |

| VDD OVP Voltage                                | V <sub>DD_OVP</sub>  | 17 (1                               | 85   | 90   | 95    | V        |

| Voltage Sense Section (VS Pin                  | )                    |                                     |      |      |       |          |

| Maximum VS Source Current Capability           | lvs_max              | - 0                                 | 2.3  | 2.9  | 3.5   | mA       |

| Output OVP threshold                           | Vvs_ovp              |                                     | 2.8  | 3    | 3.2   | V        |

| Output UVP threshold                           | V <sub>VS_UVP</sub>  | ~~                                  | 0.2  | 0.25 | 0.3   | V        |

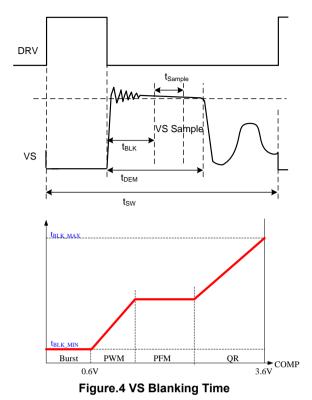

| Adaptive Blanking Time for VS Sampling         | tvs_blk              | COMP=0.5V<br>COMP=3.6V              |      | 0.6  |       | us<br>us |

| Output OVP Debounce Cycle Counts <sup>6)</sup> | Nvs_ovp              |                                     |      | 3    |       | Cycle    |

| Output UVP Blanking Time                       | tvs_uvp              |                                     | 89.5 | 106  | 122.5 | ms       |

| Auto-Restart Cycles for UVP <sup>6)</sup>      | Nuvp_HIC             |                                     |      | 4    |       | Cycle    |

| Current Sense Section (CS Pin                  | )                    |                                     |      |      |       |          |

| Max CS Offset Current                          | I <sub>CS_MAX</sub>  | VDD=20V, COMP=3.6V                  | 96   | 100  | 104   | uA       |

| Min CS Offset Current                          | Ics_min              | VDD=20V, COMP=0.5V<br>at Burst Mode | 21   | 27   | 33    | uA       |

| CS Off Threshold                               | Vcs_th               |                                     |      | 31   | 65    | mV       |

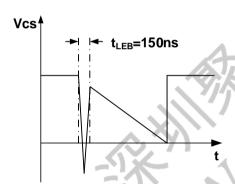

| Leading-Edge Blanking Time <sup>7)</sup>       | t <sub>LEB</sub>     |                                     |      | 150  |       | ns       |

| OCP Enable Threshold                           | Vocp_en              |                                     | 0.5  | 0.65 | 0.8   | V        |

| OCP Blanking Time                              | T <sub>OCP_BLK</sub> |                                     | 89.5 | 106  | 122.5 | ms       |

| OCP Internal Threshold <sup>6)</sup>                | Vocp                    |                                          | 0.19 | 0.2  | 0.21  | V     |

|-----------------------------------------------------|-------------------------|------------------------------------------|------|------|-------|-------|

| Auto-Restart Cycles for OCP <sup>6)</sup>           | N <sub>OCP_HIC</sub>    |                                          |      | 4    |       | Cycle |

| Frequency Section                                   |                         |                                          |      |      |       |       |

| Maximum Switching Frequency                         | f <sub>max</sub>        |                                          | 220  | 260  | 300   | kHz   |

| Minimum Switching Frequency                         | f <sub>min</sub>        |                                          | 20   | 25   | 30    | kHz   |

| Maximum ON Time                                     | Ton_max                 |                                          | 15   | 19   | 23    | us    |

| Minimum ON Time                                     | T <sub>ON_MIN</sub>     |                                          | 150  | 195  | 240   | ns    |

| Maximum Switching Cycle                             | Ts_max                  |                                          | 52   | 61.5 | 71    | us    |

| Frequency Jittering Amplitude to COMP <sup>6)</sup> | ΔFJIT                   |                                          |      | ±7%  | 7     |       |

| Counting Cycles for Jittering <sup>6)</sup>         | NJIT_CYC                |                                          |      | 32   |       | Cycle |

| COMP SECTION (COMP Pin)                             |                         |                                          |      |      |       |       |

| Open Pin Voltage <sup>6)</sup>                      | VCOMP_MAX               | Open Loop                                |      | 4.0  |       | V     |

| Internal Pull-Up Resistor <sup>6)</sup>             | Rсомр_ир                | 1 C                                      |      | 20   | 0     | kΩ    |

| COMP to CO office to compare Opin                   |                         | COMP>2.8V                                | /    | 20   | 1     | V/mA  |

| COMP to CS offset current Gain                      | GCOMP_CS                | COMP<1.0V                                | . 0  | 16   |       | V/mA  |

| The Threshold Enter PFM Mode                        | VCOMP_PFM               | 1921/34                                  | XK   | 2.8  |       | V     |

| The Threshold Enter Burst<br>Mode                   | Vcomp_bur_l             | WIND S                                   | 0.4  | 0.5  | 0.6   | V     |

| The Threshold Exit Burst Mode                       | V <sub>COMP_BUR_H</sub> | 33                                       | 0.54 | 0.6  | 0.66  | V     |

| OPP Blanking Time                                   | topp-blk                | - 60                                     | 89.5 | 106  | 122.5 | ms    |

| OPP Internal Threshold <sup>6)</sup>                | V <sub>OPP</sub>        |                                          | 0.76 | 0.8  | 0.84  | V     |

| Auto-Restart Cycles for OPP <sup>6)</sup>           | <b>N</b> орр-ніс        |                                          |      | 4    |       | Cycle |

| Over Load Protection Threshold                      | Volp                    |                                          |      | 3.6  |       | V     |

| OLP Blanking Time                                   | tolp_blk                | 0                                        | 89.5 | 106  | 122.5 | ms    |

| Auto-Restart Cycles for OLP <sup>6)</sup>           | Nolp_HIC                | <b>)</b>                                 |      | 4    |       | Cycle |

| GaN Section                                         |                         |                                          |      |      |       |       |

| Drain-source On-state<br>Resistance                 | Rds_on                  | V <sub>GS</sub> =6V, T <sub>j</sub> =25□ |      |      | 285   | mΩ    |

| Rising Time <sup>6)</sup>                           | tr                      |                                          |      | 50   |       | ns    |

| Falling Time <sup>6)</sup>                          | t <sub>f</sub>          |                                          |      | 30   |       | ns    |

| Internal Over Temperature Protection                |                         |                                          |      |      |       |       |

| Thermal Shutdown Threshold <sup>7)</sup>            | Тотр                    |                                          |      | 140  |       | °C    |

| OTP Hysteresis <sup>7)</sup>                        | T <sub>HYS</sub>        |                                          |      | 30   |       | °C    |

|                                                     |                         |                                          |      |      |       |       |

#### Note:

- 6) Guaranteed by design.

- 7) Derived from bench characterization. Not tested in production

# **PIN DESCRIPTION**

| PIN<br>VDFN6×8_8 | NAME  | DESCRIPTION                                                                                                                                                                                                                    |  |

|------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 2             | DRAIN | Drain terminal of the Internal GaN.                                                                                                                                                                                            |  |

| 3                | NC    |                                                                                                                                                                                                                                |  |

| 4                | HV    | High voltage input pin. This pin provides a source current to charge VDD. This pin is used for X-cap discharge when the AC input is removed. Besides, this pin also sense input voltage for brown-in and brown-out protection. |  |

| 5                | VDD   | Bias power input to the controller. A hold-up capacitor to GND is required.                                                                                                                                                    |  |

| 6                | COMP  | Feedback input pin for Flyback QR controller. Connect to an opto-coupler directly.                                                                                                                                             |  |

| 7                | VS    | Voltage sensing input pin. Coupled to the auxiliary winding via a resistor divider monitor the output voltage for OVP and UVP protection. This pin also detects resonant valley to implement QR operation.                     |  |

| 8                | CS    | Current sensing input pin. This pin sense the primary switch current for peak current control and OCP. Besides, this pin is used to choose OCP or OPP at the initial start.                                                    |  |

| 9                | GND   | The ground of the IC.                                                                                                                                                                                                          |  |

# **BLOCK DIAGRAM**

TBD

### **FUNCTIONAL DESCRIPTION**

The JW1565 is an offline flyback converter with GaN integrated, which features multi-mode quasi-resonant (QR) operation. The Quasi-Resonant (QR) with a limited frequency variation bounds the frequency band to overcome the inherent limitation of QR switching.

JW1565 has an inherent frequency jittering mechanism to improve the EMI performance under QR operation.

### 1. Start-up

### 1.1. High Voltage Start-up at Drain Terminal

When HV is connected to rectified AC input, the internal JFET turns on and a HV current source starts to charge VDD cap. As soon as VDD reaches turn-on threshold  $V_{DD\_ON}$  (16.5V), the internal startup circuit is disabled. The controller is enabled and the converter starts switching. The VDD turn-off threshold ( $V_{DD\_OFF}$ ) is 7.5V.

#### 1.2 Soft-Start

In the absence of a detected fault, the controller begins to work normally along with soft start. The internal soft-start time is within 4 ms with the feedback signal  $V_{\text{COMP}}$  rising gradually from the minimum level to the maximum level. Every restart up is followed by a soft start.

### 2. Normal Operation

After the controller start-up, it enters normal operation. The JW1565 realizes the output adjustment based on the feedback signal transmitting to the primary-side controller by the opto-coupler.

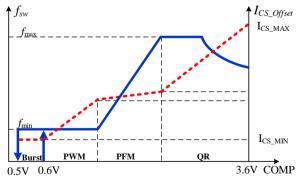

JW1565 is a multi-mode QR converter with secondary-side regulation. According to the feedback signal  $V_{\text{COMP}}$ , the converter operates

in different modes for efficiency optimization. Figure.1 illustrates the frequency and peak current amplitude modulation modes. It can be divided into four operation regions as shown in Figure.1.

Under heavy load condition, the system operates in QR mode, the maximum switching limited 260kHz. frequency is to medium-load range, the Pulse Frequency Modulation (PFM) is used and primary peak current is nearly fixed to achieve high efficiency. When the load is further reduced, switching frequency is fixed at 25kHz along with primary peak current varying from 50% to 25% of its maximum. When the system is at very light load condition, the control mode of JW1565 changes to burst mode. When the voltage of COMP pin drops below V<sub>BUR\_L</sub> (0.5V), the drive stops. The drive will resume when the voltage of COMP pin rises back to V<sub>BUR H</sub> (0.6V). Otherwise the GaN remains at off state to minimize the switching loss and reduce the standby consumption. Transitions between modes are automatically accomplished by the controller depending on the feedback signal, V<sub>COMP</sub>.

Figure.1 Frequency & Ipk Modulation

### 3. Other Functions and Features

#### 3.1 Frequency Jittering

To achieve good EMI performance, frequency jittering method is integrated in JW1565. The frequency jittering is achieved by varying the switching frequency directly. The variation is ±7% around its normal value. The modulation cycle is determined by counting consecutive 32 switching cycles.

### 3.2 Lead Edge Blanking (LEB)

In order to avoid the premature termination of the switching pulse due to the parasitic capacitance, an internal leading-edge blanking (LEB) is used between the CS pin and the current comparator input. The current comparator is disabled and can't turn off the internal GaN during the blanking time. The normal LEB time is around 150ns. Figure.2 shows the leading edge blanking time.

Figure.2 LEB Blanking

### 3.3 CCM Preventing

For JW1565, when the primary-side peak current exceeds the value decided by the feedback signal V<sub>COMP</sub>, the switch turns off. When the controller detects ZCD signal and the switch period exceeds frequency-limit signal, the switch turns on. But the ZCD signal may not be detected during start-up moment because of low output voltage, then the switch will turn on after 80us to make sure the system operates in DCM.

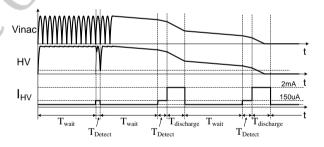

Safety standards such as EN60950 UL62368 require that any X-capacitors in EMI filters on the AC side of the bridge rectifier quickly discharge to a safe level when AC is disconnected. The standards require that the voltage across the X-cap decay with a maximum time constant of 2s. Typically, this requirement is achieved by including a resistive discharge element in parallel with the X-cap. However, this resistance causes a continuous power dissipation that impacts the standby power performance.

In order to reduce standby power and eliminate the standing loss associated with conventional discharge resistors, the JW1565 incorporates X-cap discharge circuit. This circuit periodically monitors the voltage across the X-cap to detect any possibility that AC source disconnection has occurred, and then discharges the voltage across the X-cap using the internal HV current source. The HV discharge function discharges the X-cap to the safety-voltage level in 2s. Figure.3 shows the X-cap discharge timing diagram.

Figure.3 X-cap Discharge

### 3.5 VS Blanking Time

VS spikes are affected by the amplitudes of lpk and inductance, so VS blanking time should be set to vary with lpk. Ensure that the secondary side conduction time is greater than the VS Blanking Time.

### 3.4 HV Discharge Function

4. Protection

### 4.1 CS Pin Open Protection

When CS pin is open, the internal bias current will flow to the parasitic capacitance on the CS pin, increasing the  $V_{CS}$ . If  $V_{CS}$  is above 2.0V, a CS pin open fault triggered.

### 4.2 Input Brown in / Brown out

The JW1565 senses HV voltage to realize brown in/out function. When HV voltage is higher than  $V_{BR\_IN}$  (112V typically), a 5mA pull down current will be applied to VDD pin to make VDD hit  $V_{DD\_OFF}$ . When VDD reaches  $V_{DD\_ON}$  again, the controller starts switching. And the controller is disabled when HV voltage is lower than  $V_{BR\_OUT}$  (98V typically) for brown-out blanking time (70ms typically). The blanking time is set long enough to ignore a two cycle drop out. The timer starts counting once HV voltage drops below  $V_{BR\_OUT}$ .

Figure.5 Brown-In at HV pin

### 4.3 Output OVP (VS OVP)

The output over voltage protection is determined by the voltage feedback on the VS pin. If the voltage sample on VS exceeds 3V for three consecutive switching cycles, an VS\_OVP fault is asserted, and then the device shuts down, the UVLO reset and re-start fault cycle begins.

#### **4.4 VS UVP**

If the voltage sample on VS pin continues below the under-voltage protection threshold (0.25V) more than 120ms, a VS\_UVP fault is asserted. When a VS\_UVP fault is asserted, the device shuts down and the UVLO resets. In order to reduce the power consumption of the circuit, VDD needs to hit  $V_{DD\_OFF}$  four times, and then the device restarts at the fifth cycle.

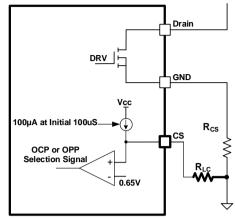

#### 4.5 OCP or OPP Selection Circuit

In some PD or QC applications, the maximum output current at different output voltage differs much. So OCP should be disabled, and the alternative OPP is enabled. JW1565 senses CS voltage at initial start to determine whether to use OCP or OPP function as Figure.6 shows. At the initial 100us, a 100uA current is applied to CS pin. If CS voltage exceeds a preset enable threshold (typical 0.65V), OPP is enabled and OCP is disabled. Otherwise, OPP is disabled

and OCP is enabled.

Figure.6 OCP or OPP Selection Circuit

#### **4.6 OCP**

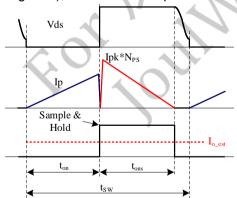

If OCP is enabled, JW1565 compares estimated output average current and OCP threshold. The output average current is calculated at the primary side. When the primary switch turns off, the peak inductor current ( $I_{pk}$ ) is sampled and hold for output current calculation.

As shown in Figure.7, it calculates output current based on secondary side current conduction time  $T_{ons}$  and primary side current information  $V_{CS}$ . If the calculated output current signal,  $I_{o\_est}$  is higher than the internal OCP threshold  $V_{OCP}$  (0.2V typically) for 120ms (OCP blanking time), IC enters OCP protection.

Figure.7 Output Current Estimation

So the OCP point can be set as:

$$I_o = \frac{V_{ocp} \cdot N_P}{2 \cdot R_{CS} \cdot N_S} \tag{1}$$

where,  $N_P$  is the turns number of primary winding,  $N_S$  is the turns number of secondary winding,  $R_{cs}$  is the current sensing resistance.

When an OCP fault is asserted, the device shuts down and the UVLO resets. In order to reduce the power consumption of the circuit, VDD needs to hit  $V_{DD\_OFF}$  four times, and then the device restarts at the fifth cycle.

#### **4.7 OPP**

If OPP is enabled, JW1565 compares estimated output power and OPP threshold. The output power is calculated at the primary side based on the output average estimated

current in OCP and the output voltage according to VS voltage. So the output power can be expressed as:

$$P_{out} = I_o \cdot V_o = \frac{V_{CS\_PEAK} \cdot D_S \cdot N_P}{2 \cdot R_{CS} \cdot N_S} \cdot \frac{VS \cdot N_S}{N_{aux}} \cdot \frac{R_{UP} + R_{DOWN}}{R_{DOWN}}$$

(2)

And the OPP point can be set as:

$$P_{out} = \frac{V_{OPP} \cdot N_P}{2 \cdot R_{CS} \cdot N_{out}} \cdot \frac{R_{UP} + R_{DOWN}}{R_{DOWN}}$$

(3)

where,  $N_{\text{aux}}$  is the turns number of auxiliary winding,  $N_{\text{P}}$  is the turns number of primary winding.

If the calculated output power signal is higher than the internal OPP threshold  $V_{\text{OPP}}$  (0.8V typically) for 120ms (OPP blanking timer), IC enters OPP protection. When an OPP fault is asserted, the device shuts down and the UVLO resets. In order to reduce the power consumption of the circuit, VDD needs to hit  $V_{\text{DD\_OFF}}$  four times, and then the device restarts at the fifth cycle.

#### 4.8 Over Load Protection

If the voltage on COMP pin continues exceeds the over-load protection threshold (3.6V

JoulWatt Proprietary Information. Patent Protected. 10 / 13

typically) more than 120ms, an OLP fault is asserted. The device shuts down, then the UVLO reset and re-start fault cycle begins.

#### 4.9 VDD OVP

If the voltage on VDD pin continues exceeds the over-voltage protection threshold (90V typically) more than 100us, a VDD OVP fault is asserted. The device shuts down, then the UVLO reset and re-start fault cycle begins.

#### 4.10 Internal OTP

The internal over temperature protection threshold is 140°C. If the junction temperature of the device reaches this threshold, the device shuts down. When the junction temperature falls below 110°C, the device initiates the UVLO reset and re-starts fault cycle.

### **PACKAGE OUTLINE**

### IMPORTANT NOTICE

Joulwatt Technology Co.,Ltd reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein.

- Any unauthorized redistribution or copy of this document for any purpose is strictly forbidden.

- Joulwatt Technology Co.,Ltd does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- JOULWATT TECHNOLOGY CO.,LTD PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, SAFETY INFORMATION AND OTHER RESOURCES, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

Copyright © 2022 JoulWatt

All rights are reserved by Joulwatt Technology Co., Ltd